캐시의 필요성

만약 저장 공간도 크면서 동시에 읽고 쓰는 속도가 빠른 메모리가 있다면 정말 좋은 일일 것이다.

하지만 아쉽게도 현실에는 그런 메모리가 존재하지 않는다.

큰 메모리는 작은 메모리에 비해 비교적 느리기 때문에, 무한히 크면서 무한히 빠른 메모리는 못 만들고 있다.

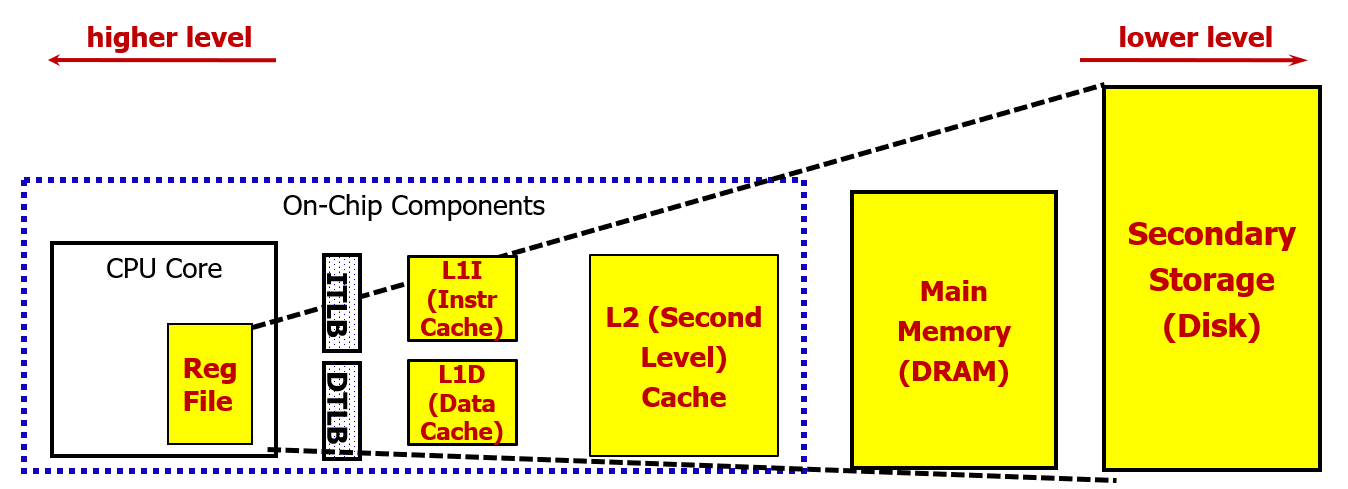

그래서 우리는 이렇게 메모리 계층을 나누어 이용하였다.

이렇게 피라미드 쌓듯이 다양한 종류의 메모리를 나누어 사용함으로써 마치 크고 빠른 메모리를 사용하고 있다는 착각을 하게 만드는 것이다.

캐시의 필요성을 정리하기에 앞서, 먼저 무어의 법칙을 살펴보자.

무어의 법칙은 정말 이론적으로 증명된 법칙이라기보다, 인텔의 창립자인 무어라는 사람이 한 예측인데, 이 예측이 워낙 잘 들어맞아서 법칙이라고 부르게 되었다.

무어의 법칙은 1980년의 DRAM과 마이크로프로세서의 성능을 1로 두었을 때, 마이크로프로세서는 1년에 55%의 성장을 해서, 1.5년마다 2배씩 성능이 증가하고, DRAM의 경우, 1년에 7% 성능이 증가해서, 10년에 2배씩 성능이 늘어난다는 것을 말한다.

그런데 그래프를 보면 알 수 있듯이, 마이크로프로세서의 성능이 증가하는 속도와 DRAM의 성능이 증가하는 속도 차이 때문에 점점 성능 간격이 벌어지는 것을 볼 수 있다. (매년 50%씩 차이가 증가)

즉, 매년 최신 컴퓨터를 살 때마다 CPU는 빨라졌는데 메모리는 왜 이렇게 느리지? 하고 느끼고 있는 것이다.

이런 현상을 '메모리 월 (memory wall)' 이라고 부른다.

방법에 따라 memory wall 문제를 그냥 어쩔 수 없다고 넘기는 방법도 있고, 극복하려고 하는 방법도 있는데, 당연히 극복하려는 방법을 사용한다.

그래서 컴퓨터 아키텍쳐들이 선택한 방법은 메모리 계층을 잘 나누는 방법을 선택했다.

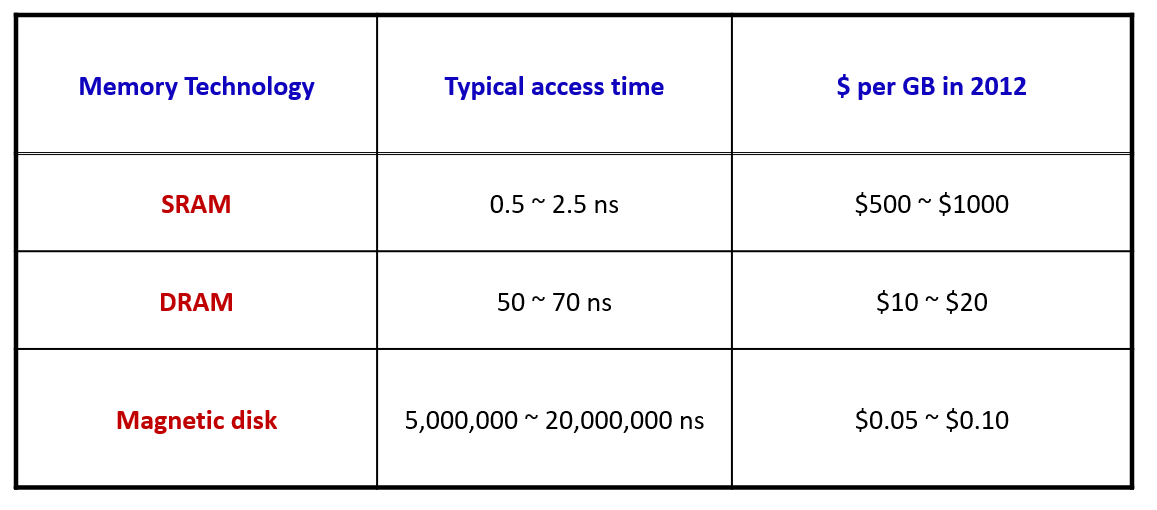

이 표는 메모리 종류마다 속도와 가격을 나타낸 표이다.

메모리는 어떻게 만드느냐에 따라 비싸지만 빠르게 만들 수도, 싸지만 느리게 만들 수도 있다.

SRAM 은 상대적으로 빠르지만 아주 비싸거나, 많이 집어넣을 수 없는 상태여서 용량이 상대적으로 작고, 디스크로 갈 수록 느려지는 동시에 점점 저렴해져서 크게 만들 수 있다.

그래서 이 메모리 기술들을 적절히 섞어서 계층을 만들게 된다.

memory wall 과 성능

메모리 월 현상은 컴퓨터의 성능에 안 좋은 영향을 미친다.

왜 그런지 예시를 한번 정리해보자.

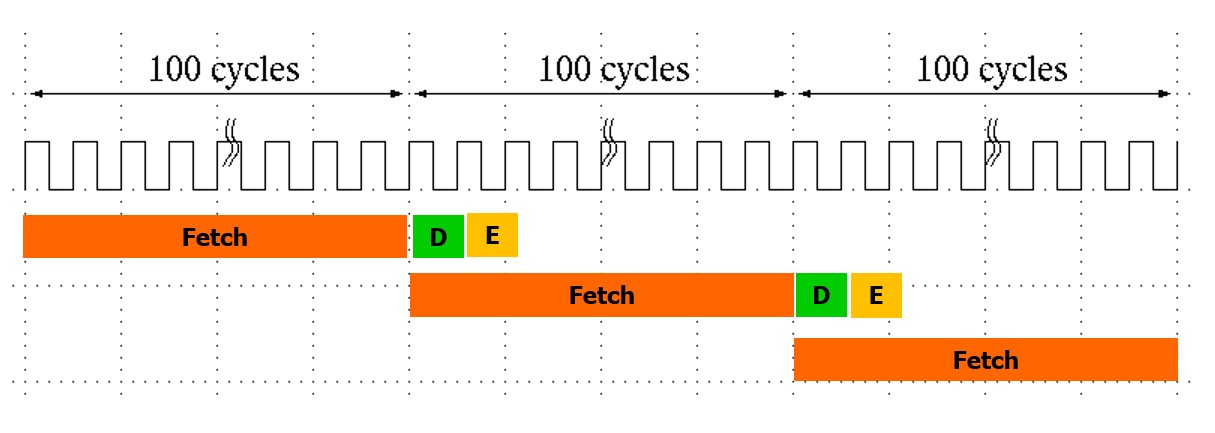

어떤 CPU의 주파수가 1GHz 라고 해보자. (주기가 1ns)

그리고 main memory에서 데이터를 읽고 쓰는데 100ns 가 걸린다고 해보자. (100 사이클)

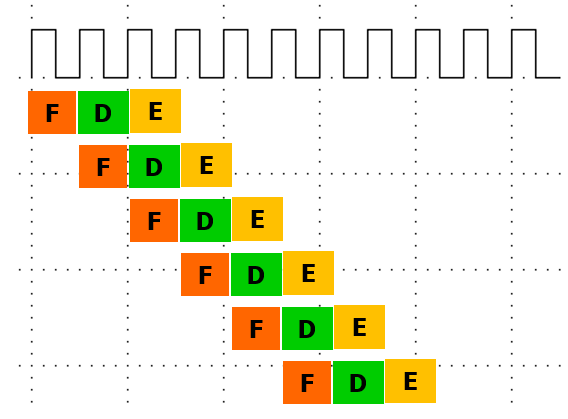

우리가 사용하는 파이프라인 CPU를 이용한다면 fetch 명령어를 이용해서 명령어를 가져오는데 100 cycle, 해석하고 실행하는데 각각 1cycle씩 소모가 되어서 위와 같은 그림이 그려진다. (예시를 위해 스테이지 3개만 표시하였다.)

즉 CPU의 성능이 빨라서 해석과 실행을 아무리 빠르게 한다고 해도, 명령어를 가져오는데 100cycle이 걸리면 전체적인 성능 (명령어 하나를 실행하는데 걸리는 시간) 은 DRAM의 성능(접근 속도)에 의해 결정되어 100cycle이 되게 된다.

따라서 CPU의 성능이 아무리 증가해도 메모리 성능이 증가하지 않으면 이 속도는 줄어들지 않을 것이다.

게다가 이 문제는 시간이 지날 수록 점점 더 심해진다.

무어의 법칙에 의하면 메모리의 성능이 증가하는 속도보다 CPU의 성능이 증가하는 속도가 더 커서 이 간격이 더 증가하기 때문이다.

캐시의 도입

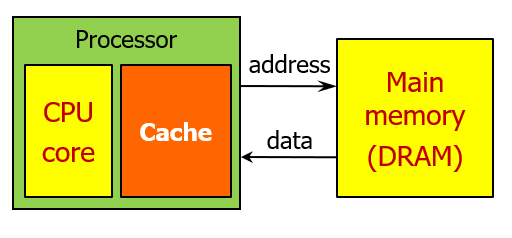

그래서 이 문제를 해결하기 위해 파이프라인 아키텍처 외에도 캐시를 추가로 도입하였다.

캐시는 일종의 메모리이다. 캐시는 DRAM 과 CPU 사이의 성능 간극을 줄이기 위해 도입되었다. 따라서 캐시는 그림에서 보는 것처럼 항상 프로세서 내부에 들어가있다.

프로세서 내부에서 직접 CPU와 소통하기 때문에 DRAM보다 접근하는 속도가 빠르지만, 프로세서 내부라는 한정된 공간안에 넣어야 하기 때문에 용량은 상대적으로 작다.

캐시는 어떤 메모리를 사용해서 만들어야 한다고 정해진 것은 없지만, 보통은 SRAM을 이용해서 만든다.

어떤 프로그램을 실행하게되면 그 프로그램의 명령어들이 메인 메모리에 로딩이 된다.

이렇게 로딩된 프로그램을 '프로세스' 라고 부른다.

하지만 DRAM에 있는 데이터와 명령어를 캐시에 모두 넣을 수는 없다.

따라서 자주 사용되는 명령어와 데이터를 골라서 캐시에 저장하게 된다.

(예를 들어 for문을 10000번 돌린다고 하면, 반복의 기준이 되는 변수 i와 같이 반복문 내부에서 사용되는 변수들은 10000번 접근하게 되므로 캐시에 저장하는 것이 효율적이다.)

그리고 자주 사용되는 명령어와 데이터는 '하드웨어'에 의해 선별되어 들어간다.

내가 작성한 프로그램이니까 어떤 게 자주 사용되는지 내가 안다! 내가 캐시에 직접 넣겠다! 라고 하고 싶어도 캐시는 프로그래머가 접근해서 쓸 수 있는 하드웨어가 아니다.

캐시에 들어가고 나오는 값은 하드웨어가 결정하며 프로그래머는 관여할 수 없다.

캐시는 그 자체로 메모리의 계층을 차지하기 때문에, 레벨이 나뉘어져 있다.

레벨1이 CPU와 제일 가까운 캐시이며, 요즘은 레벨 4 캐시까지 나온다고 한다.

이때 레벨1 캐시가 제일 작고, 제일 빠르다.

그리고 레벨 1 캐시는 일반적으로 1 cycle에 동작시킬 수 있도록 만들어져 있다.

그러면 앞서 봤던 성능 그래프를 아래와 같이 그릴 수 있게 된다.

그러면 이제 CPI는 1에 수렴하게 되어 파이프라인을 올바르게 운용할 수 있게 된다.

SRAM vs DRAM

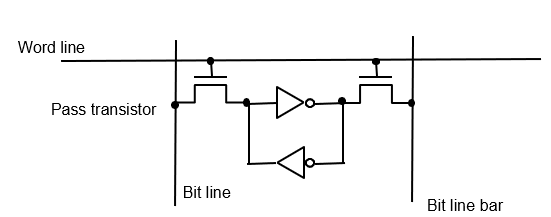

SRAM은 그림과 같은 구조로 되어있다.

이 구조가 1bit 데이터를 저장하는 SRAM 구조이다.

여기에서 어떤 부분은 트랜지스터로, 어떤 부분은 인버터로 그려져 있다.

(이 내용은 시험 범위가 아니라서 잠시 정리를 미루도록 한다. 컴구 12-3, 27분 34초, 슬라이드 Lec 15 6페이지)

위 그림은 DRAM의 구조이다.

비교적 SRAM보다 단순한 구조로 되어 있다.

결론은 DRAM은 만드는데 트랜지스터를 상대적으로 적게 쓰고, SRAM은 상대적으로 많이 써서 가격 차이가 난다.

CPU 내 캐시 위치

컴퓨터의 보드를 위와 같이 나타낼 때, 캐시는 Processor 안에 있다.

다시 프로세서를 확대해서 보면 위와 같이 코어가 2개 있고, 각각의 코어에는 Structure Hazard를 해결하기 위해 Instruction Level1 Cache, 와 Data Level 1 Cache가 하나씩 들어있다. (Level 1 캐시는 코어에 종속되어 있다. 이렇게 각 코어가 자신이 개인적으로 사용하는 캐시를 Private Cache 라고 한다.)

그리고 두 코어가 공통으로 사용하는 Level 2 Cache가 들어있다. (이런 공용 캐시를 Shared Cache 라고 한다.)

이 그림에서 L2 캐시는 전체 프로세서의 절반이라는 공간을 차지하고 있고, 4MB의 용량을 갖고 있다.

이 용량을 갖는 메모리를 만들기 위해서는 32메가비트의 공간이 필요하고, SRAM을 사용하는 경우, 여기에 6을 곱해서 192 * 100만 개의 트랜지스터를 사용해야 한다.

이 이미지는 Intel Core i7 2세대의 모습이다.

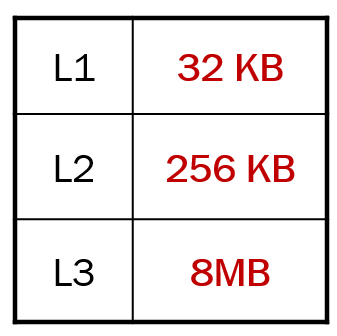

이 경우 L3 캐시는 shared 캐시이고, 쿼드코어로 구성된 각각의 코어 내에는 L1, L2 캐시가 프라이빗 캐시로서 들어가있다.

그리고 각 캐시 용량은 위와 같다.

Memory Hierarchy

지금까지 정리한 내용을 토대로 메모리 계층을 나누면 다음과 같이 나타난다.

CPU 코어에는 레지스터가 있고, 칩셋 내부에 L1 캐시가 2종류 (Instruction, Data), L2 캐시가 들어있다.

L2캐시까지는 칩셋 내부에 있어서 on-chip 이라고 부르고, Main Memory는 off-chip 메모리 라고 부른다.

중간에 있는TLB (ITLB, DTLB)는 Table Lookup Side Buffer 라고 부르는 메모리로, 나중에 정리한다.

이런 계층 구조는 locality 원칙의 이점을 얻을 수 있게 해준다.

이를 통해 작지만 빠른 메모리를 계속해서 사용할 수 있다.

그러면 이렇게 계층을 나누었을 때, 각 계층간에 데이터를 주고받는 일은 누가 관장할까?

먼저 레지스터와 메인 메모리 사이의 데이터 전달을 생각해보자.

이 부분은 lw, sw 와 같은 명령어를 사용해서 프로그래머가 (컴파일러가) 직접 관리할 수 있다는 것을 알 수 있다.

반면 캐시와 메인 메모리 사이의 데이터 전달은 어떻게 일어날까?

상술했듯 이 과정은 프로그래머가 전혀 건들 수 없으며, 'cache controller' 라는 하드웨어에 의해 관리된다.

'CS > 컴퓨터 구조' 카테고리의 다른 글

| [컴퓨터 구조] 25. Cache (3) - 성능 개선 (0) | 2024.06.06 |

|---|---|

| [컴퓨터 구조] 24. Cache (2) - Direct-Mapped Cache (0) | 2024.06.04 |

| [컴퓨터 구조] 22. Pipeline MIPS (6) - 성능 측정 (0) | 2024.06.03 |

| [컴퓨터 구조] 21. Pipeline MIPS (5) - 회로 개선 (Control Hazard) (0) | 2024.06.02 |

| [컴퓨터 구조] 20. Pipeline MIPS (4) - 회로 개선 (Data Hazard) (0) | 2024.06.02 |